## What is an Embedded Processor?

- An Embedded Processors is simply a uProcessors that has been "Embedded" into a device

- It is software programmable but interacts with different pieces of hardware how?

- Performs both control and computation more performance than a uController but not as much performance as a general purpose processor... yet

- Where are they used: Cars, Phones, Media Devices, Wireless, Printers – everyone uses them without thinking about it – start to think about it

San Diego

CSE291E/EE260 5

Why use an Embedded Processor?

- If I am John Q. RandomEngineer why would I want to build a system with an embedded processor built in?

- The main reason is simple: Cost

- Embedded processors are small so they don't take up much die area and thus they are cheap to fab

- Embedded processors are verified so I won't spend a bunch of engineering man hours traking down hardware bugs so I can tape out my chip

- Embedded processors run software the key part of that is the SOFT – deal with changing specs

San Diego

CSE291E/EE260 7

## Design Criteria

- · How do I design an "good" embedded processor?

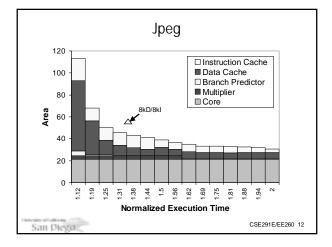

- The three most important design criteria are performance, power, and cost.

- Performance is a function of the parallelism, instruction encoding efficiency, and cycle time (or the good old NumInstr, CPI, Freq)

- Power is approximately a function of the voltage, area, and switching frequency

- Also a function execution time for leakage

- Cost is a function of both area (how many fit on a die) and the complexity of use (in terms of engineering cost)

San Diese

- TLB

- Branch Prediction

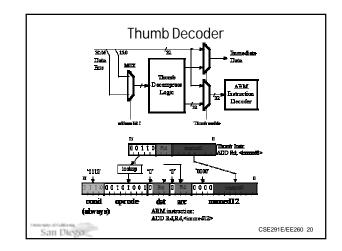

- Thumb code is 65% of the size of ARM code,

- · Lets software be designed for performance or code size on the granularity of a basic block - flexibility.

- Harvard Architecture (8k Icache, 8k Dcache)

- 5 Stage Pipeline

- · Improved MMU support

- 8 entry write buffer

- In 0.13µm:

- Die size of 3.2 mm<sup>2</sup>

- Greater than 250 MHz

- IPC of 1.1

- 0.36/0.19 mW/MHz (with/without cache)

CSE291E/EE260 23

## ARM10

- New 64-bit load-store architecture

- Up to 32K instruction and data cache

- 7 Stage pipeline

- New DSP instruction set

- · Optional Vector Co-processor

- In 0.13µm:

- Die size of 6.9 mm<sup>2</sup>

- Greater than 325 MHz

- IPC of 1.25

- 0.6 mW/MHz

San Diego

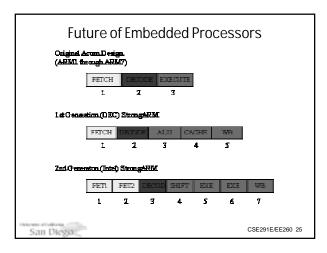

## Future of Embedded Processors VLIW processors Multiple issue machines Scheduling done by the compiler Customized Processors Such as from Tensilica Allows more cost effective design as we now pick only what is important Instruction Compaction Thumb is good, but we need to do better as more and more functionality moves to software

San Diego